無安定マルチバイブレータによるVGAの水平垂直同期信号の生成

2025-08-06

カテゴリ:電磁気

7400NANDゲートによる無安定マルチバイブレータでいわゆるVGA(画面解像度640x480)に簡単な映像出力がでるのではないか と思ったので製作してみた.

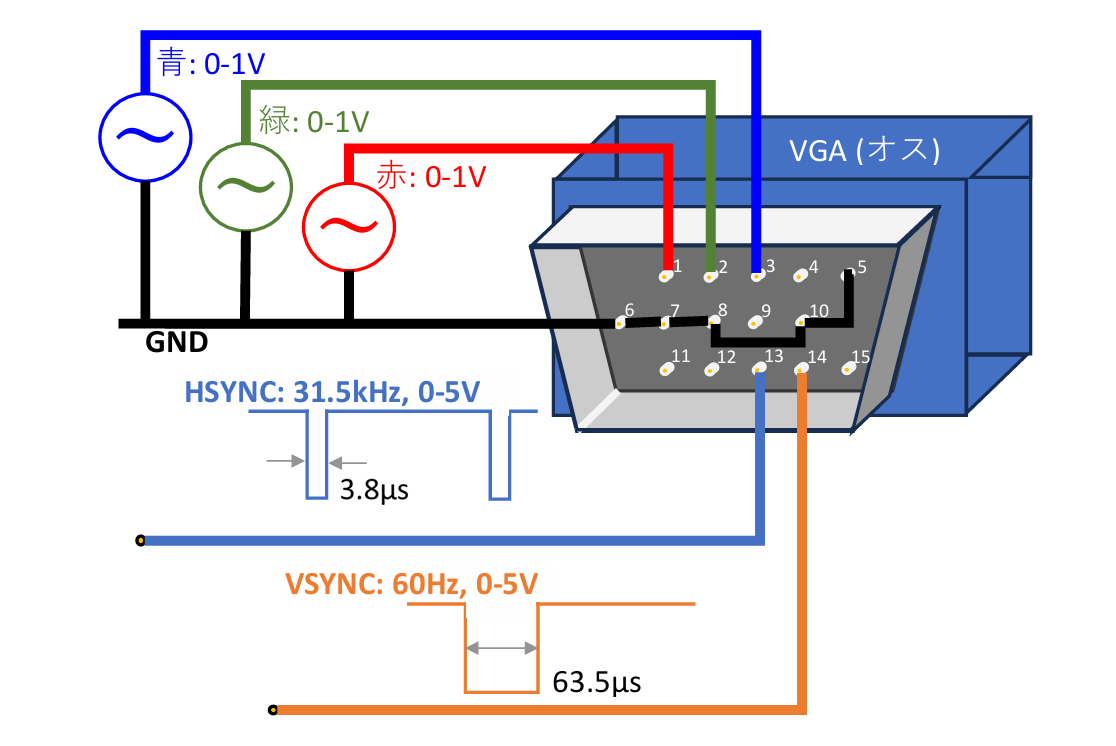

図0 VGAのピン配置と信号

要旨

VGAを成立される信号には細かい規定があるが(参考文献:TinyVGA ),要点は- 水平同期信号 (H-SYNC): 31.5kHz, アクティブLow, TTLレベル(5V), パルス幅 3.8μsec

- 垂直同期信号 (V-SYNC): 60Hz, アクティブLow, TTLレベル(5V), パルス幅 63μsec D-SUB15端子の13ピン

- 走査線の本数 (=垂直方向の解像度) = 31.5k/60 = 525本

- R,G,B各チャンネル: 0~1Vの範囲で表すアナログ信号.入力インピーダンス75Ω

- 端子とピン配置: D-SUB15ピン.1:Red,2:Green, 3:Blue, 5,10:GND,13:H-SYNC, 14:V-SYNC. なお,VGAの規格ではチャンネルごとに独立のGNDを取れるようになっており,6:Red Return, 7:Green Return, 8:Blue Returnが割り当てられているが, 5,10,6,7,8を短絡してGNDと接続とすれば十分である.

- NANDゲート (7400) でH-SYNCまたはその数倍の周波数をもつクロックを構成する(本制作では,31.5kHz x 4 = 126KHzとした). 周波数を決める抵抗を可変抵抗器とし,オシロスコープで観察してチューニングする.

- バイナリカウンタ (74163) でクロックを分周して,31.5kHz (4分周), 61.52344Hz (4x512分周)を作り出す. もちろん,走査線525本なので,ただしくは,4x525分周する必要がある.それは,バイナリカウンタの 出力が"525"になることを検知して,リセットを掛けるがモニタ側が受容してくることを期待して,512で近似した.

- パルス微分回路 (NAND + RC積分回路)でパルス幅を調整.

- カウンタでの分周の過程で生じる中間周波数 (15750Hz, 7875Hz, ...)を適当に選んでR,G,B信号をつくる. たとえば電源電圧(Vcc)5Vの場合,330Ω抵抗を介して各ピンに接続すると,モニタ側に掛かる電圧は 75/(330+75)*5 = 0.92V となり,最大輝度に近い出力になる.

回路図

要旨で述べた戦略に沿って実装した回路を図1に示す.ただし,各IC左上の電源ピンとGNDの間に追加した パスコン1μFと中間周波数から色信号を作る部分は省略した. 分周に用いた3つの74163のoA~oDに中間の周波数の矩形波が出力される. このどれかを抵抗をはさんで,D-SUB15の1,2,3ピンでに差し込むとR,G,B各チャンネルの色信号が作られる.

実装上の注意点や回路定数の選択などは以下のとおり

- クロック生成 NANDゲート1,2を使って無安定マルチを構成する.コンデンサ \(C_1 = 1{\rm \,nF}\),可変抵抗 \(R_1 \le 20{\,\rm kΩ}\)とすると 周波数は \( f \ge \frac{1}{2.2 R_1 C_1} \approx 45\,{\rm kHz} \)となる.目標の126kHzに対し 低すぎるが,当初はH-SYNCのもとになる31.5kHzの矩形波をつくるつもりだったので,この設計となった.

- カウンタによる分周 74163同期型4桁バイナリカウンタ3つをカスケード接続して 12桁カウンタを構成し,NANDゲート2の出力(126kHz)を60Hzまで分周する. このICはCLKのLowからHighへの変化 をイベントとしてカウントする (そのためクロックとカウンタの桁は同期してHighからLowに遷移できず, クロック自体をH-SYNCにできない). カウントの結果,一番左のICのoBに31.5kHz,一番右のoCに60Hzが現れる. ただし,これは等幅パルスなので,幅を狭める処理が必要である. カスケード接続するにはRCをEnTに入力する.今回,カウンタは常時 稼働させ,データの読み込みもしないのでEnPと\(\overline{\rm LOAD}\)はHighに接続する.

- パルス幅調整

立ち下がりを検知してパルスを出力するによく使われる回路である.

入力信号 \(s(t)\) に対し,\(\overline{s(t)} \wedge s(t - \tau)\) は

\(s(t)\)の立ち上がりから期間 \(\tau\) だけ High となる.しかし,

立ち下がり型の同期信号を求められているので,さらに否定をとり \(\overline{\overline{s(t)} \wedge s(t - \tau)}\)

を出力する.この演算はNANDゲート2つで実行できる.時間遅れ(\tau)はRC積分回路で実装する:

\(\tau = \ln(2)CR \approx 0.7 CR\).

採用した定数と目標値は以下のとおり

- H-SYNC: \(C_2 = 1\,{\rm nF}, R_2 \le 10\,{\rm kΩ}\) より \(\tau \le 7{\rm \,μs}\) (目標 3.8μs)

- V-SYNC: \(C_3 = 47\,{\rm nF}, R_3 \le 10\,{\rm kΩF}\) より \(\tau \le 470{\rm \,μs} \) (目標値 63μs)